为了知足某大型旋希望械筑立正在监测流程中及时性高精度多通道的搜集需求,提出了一种基于FPGA的多通道振动信号搜集检测体例的打算计划。体例采用主/从式FPGA架构,正在强噪声境遇下完毕了采样频率为100 kHz的128通道并行及时数据搜集功用。然后通过打算一种参数可调的随机共振信号检测体例,普及了信号信噪比,巩固了体例正在转动境遇下检测的切确性。

中文援用花式:易志强,韩宾,鲜龙,等. 转动境遇下基于FPGA的多通道数据采团体例打算[J].电子技能操纵,2019,45(9):60-64.

跟着今世工业的飞速生长,人们对转动筑立的需求愈加紧急,如风力发电、大型炼钢筑立等转动筑立的操纵。大型旋希望械筑立固然极大地普及了临蓐率,但其突发性的窒碍率偏高,一朝停机就会形成较大的吃亏 [1]。巩固对旋希望械的状况检测和诊断职责,有帮于裁汰旋希望械窒碍率,大幅度低重板滞的维修用度和缩短维修年光,普及筑立运转的经济效益。守旧的多通道振动信号采团体例多以DSP和ARM行为限度中枢,存正在功用简陋、通道数少、时钟频率低和及时性差等污点 [2-3]。

与DSP和ARM比拟,FPGA正在数据搜集规模发扬着要紧的效用。FPGA拥有时钟频率高、内部延时幼、运算速率疾、斥地周期短、抗作对材干强、编程设备灵便、内部资源丰饶等甜头,异常合用于数据高数搜集和照料 [4-6]。本文提出了一种基于主/从式FPGA架构的128通道振动信号检测计划,体例采用了高精度A/D芯片AD7606,同时集合了FPGA的并行数据照料材干完毕了搜集信号的随机共振检测,包管了采团体例的切确性和褂讪性。

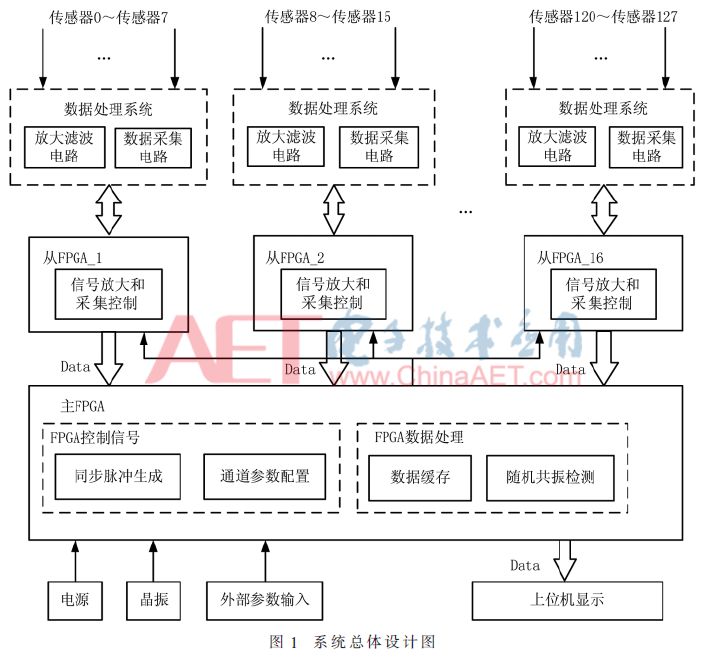

本体例总体打算如图1所示,体例由信号疗养体例、FPGA限度体例和FPGA数据照料体例三个别组成。此中信号疗养体例由放大滤波电道和AD7606搜集电道组成,紧要完毕将传感器发出的微幼信号实行放大和滤波后发送到AD7606芯片中,将搜集到的模仿信号转化为数字信号。FPGA限度体例由主FPGA限度体例和从FPGA限度体例两个别构成。从FPGA限度体例由16片Xilinx公司临蓐的Spartan3系列的FPGA组成,紧要完毕程控放大器AD8250和AD8253的信号放大限度和AD7606同步数据搜集限度。主FPGA限度体例由Xilinx公司临蓐的Spartan6系列的FPGA组成,紧要完毕参数设备、同步时钟临蓐、数据缓存等。FPGA数据照料体例由主FPGA完毕数据的时序统造和随机共振检测照料功用,通过采用主从式FPGA架构,合理分派FPGA资源,完结通盘体例的劳动安排,取胜FPGA输出时的亚稳态景象,使得体例拥有功能褂讪、数据照料材干强、抗作对性好等特色。

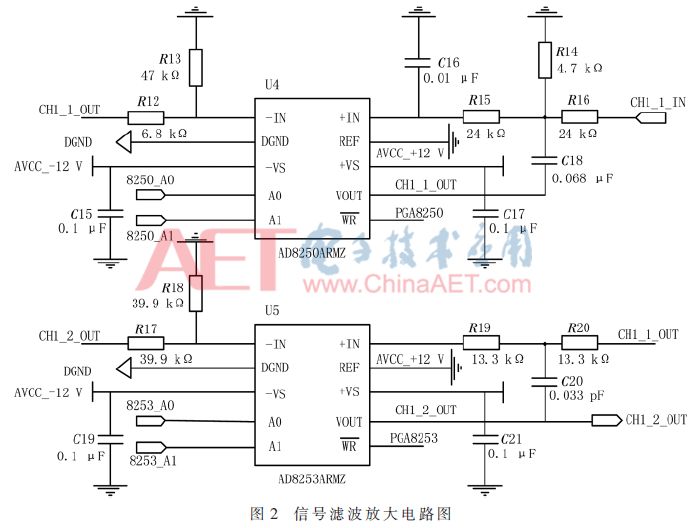

因为传感器输出信号规模蕴涵±0.025 V、±0.05 V、±0.1 V、±0.5 V 4个挡位,为包管搜集精度,不行同时对通盘量程实行放大,必要采纳分级放大的形式,且增益可调。本体例采用图2所示的两级放大电道构造,因为体例通过滑环实行供电,正在强噪声境遇下传感器输出信号起首操纵AD8253和AD8250完毕四阶的巴特沃斯低通滤波器普及信噪比。

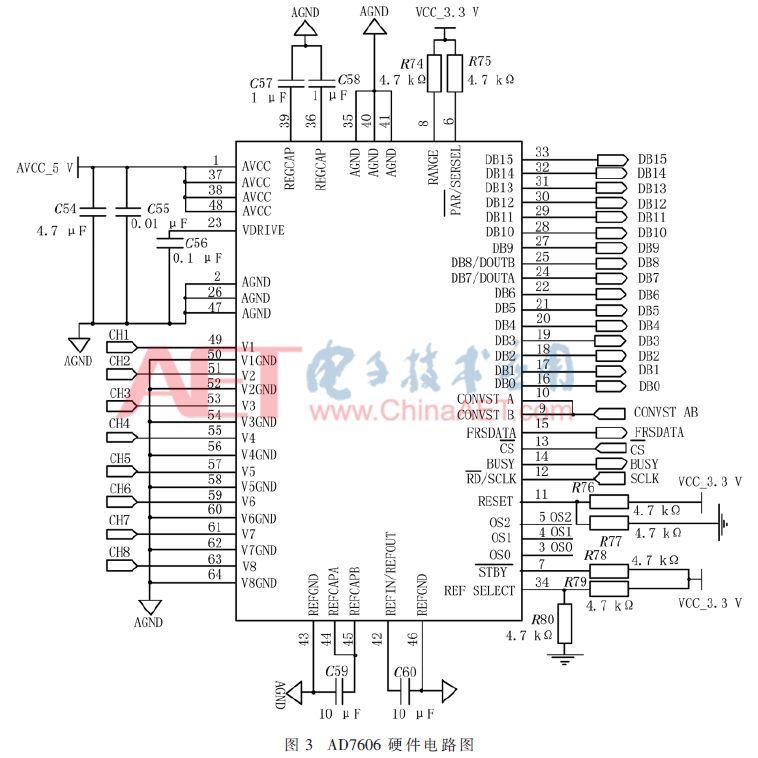

A/D数模转换器是通盘采团体例的中枢,影响着体例的搜集精度、搜集速度和数据模糊量,以是A/D芯片选型是采团体例中最环节的一步。体例采用ADI公司的高精度、低功耗、电荷再次分派逐次迫近型模数转换芯片AD7606。该产物是一款8通道16位真差分拥有二阶抗混叠模仿滤波电道的同步采样模数转换芯片。本体例采用16片AD7606芯片组成128通道的数据搜集电道。AD7606硬件电道打算如图3所示,将转换芯片CONVST A与CONVST B短接正在一同并施加统一个转换信号可以完毕8通道的数据同步转换。

FPGA软件打算紧要划分为主FPGA限度体例和从FPGA限度体例两个别。此中,主FPGA限度体例紧要完结同步时钟天生、参数设备、数据缓存、随机共振检测等功用。而从FPGA紧要完结数据组帧、程控放大限度和AD7606数据搜集限度等。下面临个别中枢模块的打算实行先容。

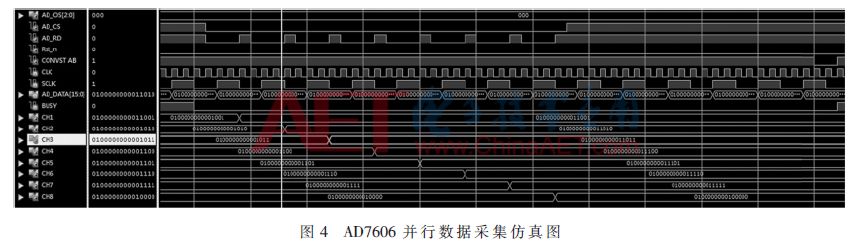

传感器发作的微幼信号源委滤波放大电道后,将其输送入AD7606芯片完毕数据搜集功用。FPGA紧要限度AD7606的转换信号CONVST AB、片选信号CS和时钟信号SCLK,完毕芯片的采样率调动和采样启停功用。如图4所示,本模块通过限度AD7606职责正在并行数据输出形式下,完毕了体例正在转动境遇下采样率为100 kHz的高速搜集功用。从仿真图中能够看出,采用并行输出的形式可以褂讪有用地将模仿信号转换为数字信号实行照料,源委多次测试注解,通过采用并行数据输出的形式,该芯片的采样偏差幼于0.1%。

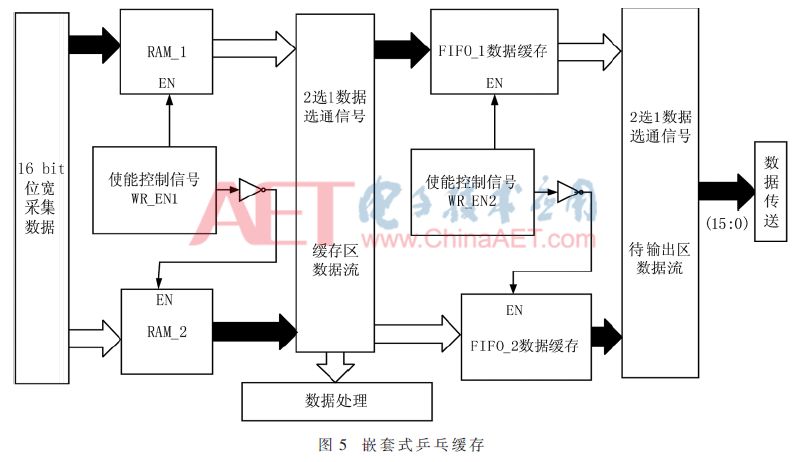

因为本体例为128道振动信号采团体例,每完结一次搜集会发作豪爽的待照料数据,因而,打算了一种嵌套式的乒乓传输缓存形式,完毕体例所需及时性数据搜集功用。比拟于守旧的乒乓式缓存 [7],其成果更高,适用性更强。如图5所示,本模块有用地操纵FPGA内部IP核资源发作两个区此表块随机存取存储器(Random Access Memory,RAM)和先入先出部队(First Input First Output,FIFO)实行嵌套式的乒乓缓存。通过筑树两个区此表使能信号WR_EN1和WR_EN2,完毕了块RAM_1、块RAM_2之间的乒乓缓存和FIFO_1、FIFO_2之间的乒乓缓存。云云循环不息,组成了嵌套式乒乓缓存。通过数据缓存模块能够很好地妥洽数据流正在各模块之间褂讪、及时有用地传输和照料。

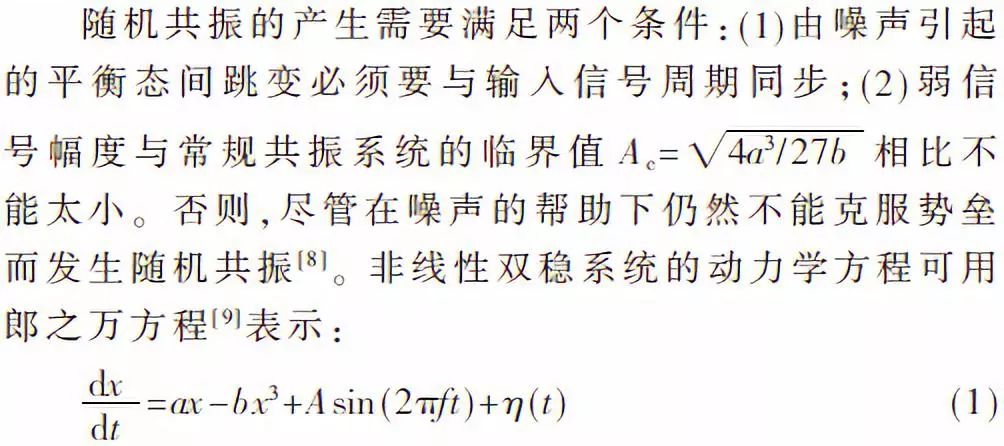

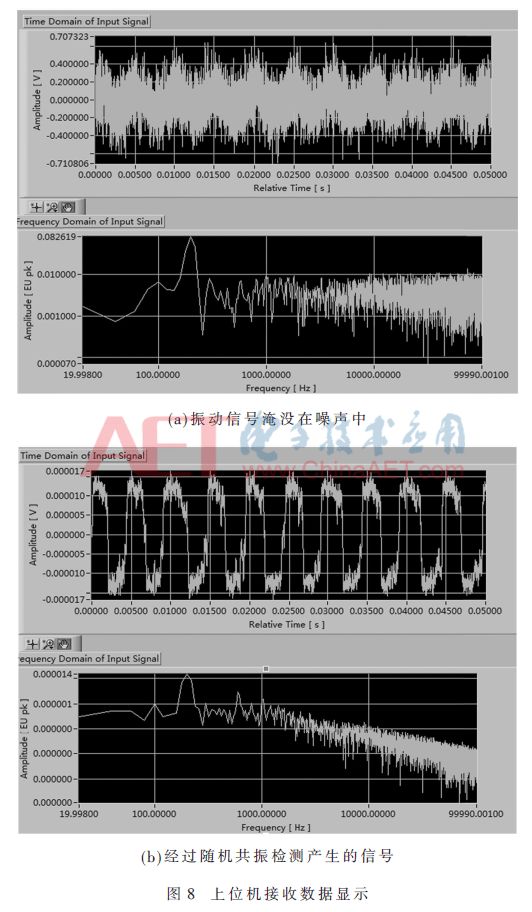

因为体例处于强噪声作对的境遇下,固然增添了四阶的巴特沃斯低通滤波电道,但正在实质工程中转动境遇下仍是会发作豪爽的无法滤除的噪声信号使有用的振动信号湮灭正在噪声中,无法平常检测。以是采用随机共振的检测伎俩,正在参数结婚的境况下将能量从噪声转化到有效信号中,使得输出信噪比普及。下面顺次从随机共振的MATLAB仿真和FPGA完毕两个方面实行先容。

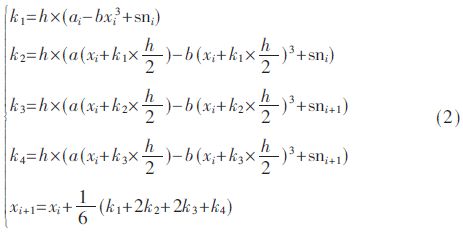

为了获得随机共振的输出,体例采用4阶龙格-库塔数值伎俩对式(1)实行求解 [10],其算法如式(2)所示:

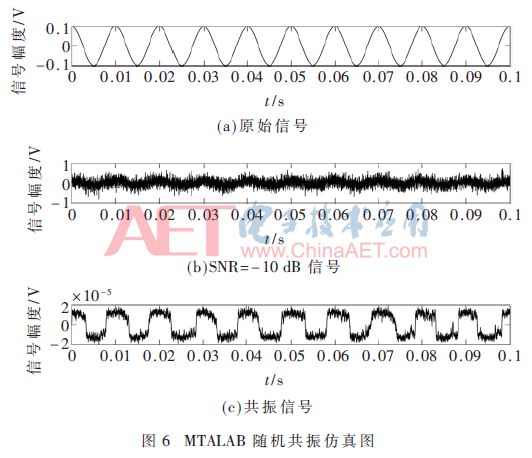

此中,xi透露x(t)的第i个采样点,sni透露对输入信号的第i个采样点,筹算步长h=1/f,f是对信号s(t)=Asin(2πft)+η(t)的采样频率,k为调动系数。随机共振的MATLAB仿线所示,从上到下分辨为原始有用信号、有用信号湮灭正在噪声中和随机共振检测输出。由仿真图可知,通过采用随机共振检测能够普及输出信号的信噪比。

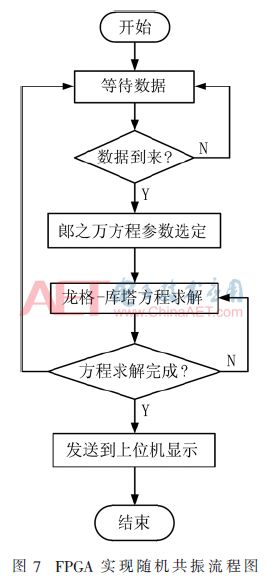

随机共振检测算法由主FPGA通过采用补码表面的定点数来完毕郎之万方程的求解,体例采用4阶龙格库塔的迭代形式,操纵FPGA的并行数据照料材干完毕了湮灭正在噪声中的振动信号的随机共振检测,本模块的流程图如图7所示。将求解出的数据发送到上位机实行及时显示,图8(a)是未操纵FPGA完毕的随机共振检测算法,由图可知有用信号一律湮灭到噪声中,无法识别。图8(b)反应湮灭正在噪声中的有用信号源委随机共振模块后检测出原有振动信号的频率,巩固了输出信号的信噪比。

针对旋希望械筑立正在强噪声境遇下难以检测的题目,本文打算了一种基于FPGA的128通道振动信号搜集检测体例,通过采用主/从式FPGA架构,极大地发扬出了FPGA的并行数据照料材干。体例采用了嵌套式的乒乓缓存形式,完毕了数据的及时缓存和传输功用;然后,采用了FPGA正在定点数补码表面下的随机共振检测,巩固了传感器有用信号的信噪比,对大型旋希望械的板滞损耗和断轴预判有着极其要紧的效用。本体例已得胜操纵于某旋希望械的监测项目中,拥有必然的适用代价。

[1] 佟庆彬,马惠萍,刘丽华,等.高速旋希望械径向振动检测体例环节技能研讨[J].仪器仪表学报,2011,32(5):1026-1032.

[2] 李静.多通道高精度数据搜集模块的打算[D].成都:电子科技大学,2018.

[3] 索艳春.面向多通道同步数据搜集存储体例的打算与完毕[D].太原:中北大学,2017.

[5] 夏宇闻.Verilog数字体例打算教程[M].北京:北京航空航天大学出书社,2005.

[7] 张素萍,李朝强,张筑芬.一种高速及时数据搜集照料体例打算[J].火力与指示限度,2016,41(7):125-129.

[9] 樊养余,李利品,党瑞荣.基于随机共振的轻易大频率微幼信号检测伎俩研讨[J].仪器仪表学报,2013,34(3):566-572.

[10] 王日明,刘明华,盛堰,等.基于龙格库塔算法和可编程门阵列技能的混沌体例完毕[J].西南师范大学学报(天然科学版),2012,37(1):41-46.

(西南科技大学 音讯工程学院,四川 绵阳621010),

支付宝转账赞助

支付宝扫一扫赞助

微信转账赞助

微信扫一扫赞助